- cross-posted to:

- [email protected]

- cross-posted to:

- [email protected]

2nm is already there? That’s crazy, I thought we just got to nodes under 10nm.

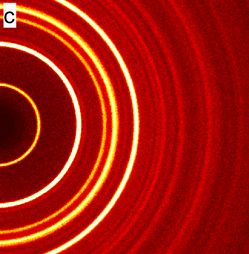

EUV was really hard to crack, but now that they have it working, refinements seem to be going well.

Also, the size of features hasn’t actually shrunk all that much from 32nm. What has really improved is the geometry of the transistors and wiring. This allows them to pack many more transistors in the area even if the lithography resolution hasn’t actually increased 16 fold. The 2nm name is just describing the relative increase in transistor density compared to the old layouts and densities.

ASML, TSMC and Intel are doing great work though. My comment is not meant to diminish what they’ve accomplished.

Good info, but damn that’s a hard article to read.

Come on its a walk in the park, everyone knows that Nanosheet GAA transistors behave differently than familiar FinFETs, so EDA and other tool and IP makers had to build their products from scratch. ¯_(ツ)_/¯

literally second grade knowledge

Second grade? That’s kindergarten shit, get outta here.

You guys had to learn this? This knowledge was instinctually given to me at birth.

Just like how smooth a sharks skin is

deleted by creator

I like all of the arguments in the comments haha